## Improving the world of DCC

- > Control signals on your layout

- > Compatible with the SHD2

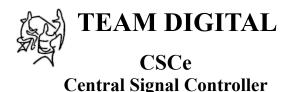

- > 16 inputs for sensors/switches

- > 16 outputs to drive LEDs

- > 2 outputs to drive servos

- > Customizable logic

- > DCC gateway to serial bus

- > LocoNet compatible

# Description

The CSCe (Central Signal Controller) is uniquely suited to control the SHD2 (dual signal head decoder) for a complete model railroad signal system.

Using block occupancy and switch state information with the CSCes build-in customizable logic allows for various types of prototypical signal arrangements to be implemented without using a computer.

Inputs are available for block occupancy information and switch state information. Outputs can be used for LED indicators on a layout or CTC panel such as block occupancy and switch (turnout) position or Tortoise<sup>TM</sup> motor control.

The serial bus is used to provide control to the SHD2 and communicate with other devices in the system. The number of wires to implement a signal system is greatly reduced when using the CSCe and the SHD2.

The serial bus is based on Digitrax's LocoNet and some features are unique to a Digitrax system. However, a Digitrax DCC system is not required for operation or programming. The CSCe is compatible with LocoNet block detectors such as the Team Digital BlocD8 or detectors connected to its inputs such as the Team Digital DBD22.

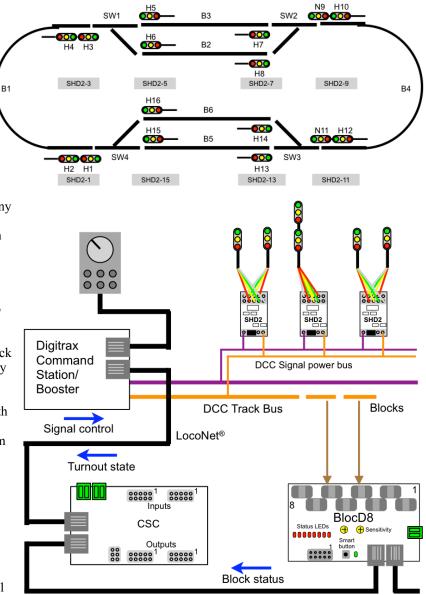

**Note:** In order to utilize all the CSCe features, JMRI DecoderPro is required for programming via the serial bus. LocoBuffer USB is shown as the interface for the computer to the serial bus. This manual assumes you know something about DecoderPro.

07.18.16 V1 LocoNet is a registered trademark of Digitrax Inc

**TEAM DIGITAL, LLC** 3111 Timber Valley Dr Kokomo IN 46902 www.teamdigital1.com

| 1 | Overview                               | 3  |

|---|----------------------------------------|----|

|   | 1.1 LED Indicators                     | 3  |

| 2 | Getting Started                        | 3  |

|   | 2.1 Programming                        | 4  |

| 3 | Operation                              | 5  |

|   | 3.1 Signal Logic                       | 5  |

|   | 3.2 The Logic Cell                     | 6  |

|   | 3.4 Logic Cell Base Address            | 7  |

|   | 3.5 CSCe Configuration                 | 7  |

|   | 3.6 Output Control                     | 8  |

|   | 3.7 Input Control                      | 8  |

|   | 3.8 Servo Configuration                | 9  |

|   | 3.9 Logic Cell Delay                   | 9  |

| 4 | Setup                                  | 10 |

|   | 4.1 Setup 1 - Four blocks              | 10 |

|   | 4.2 Setup 2 - Loop with two sidings    | 11 |

|   | 4.3 Setup 3 - APB signals              | 11 |

|   | 4.4 Setup 4 - Grade crossing           | 12 |

| 5 | Special Features                       | 12 |

|   | 5.1 Reset the CSCe to factory defaults | 12 |

|   | 5.2 Temporary Ops Mode                 | 12 |

|   | 5.3 Set Ops Mode Address               | 12 |

| 6 | Connections                            | 13 |

|   | 6.1 Power                              | 13 |

|   | 6.2 Input Interface                    | 13 |

|   | 6.3 Output Drive                       | 13 |

|   | 6.4 Input and Output Pins              | 13 |

|   | 6.5 Serial Bus                         | 14 |

| 7 | Wiring Diagram                         | 14 |

|   | 7.1 Wiring Examples                    | 14 |

| 8 | Reference                              | 16 |

|   | 8.1 Selected CVs                       | 16 |

# **1** Overview

The CSCe is designed to control SHD2 dual signal head drivers. It has built-in signal control logic (logic cells) so it is a stand-alone system. A computer is not required. Signal logic typically requires block occupancy, turnout state and signal head state information. The CSCe has inputs and a serial bus that is used to receive this information. Information received through the inputs is put on the serial bus. All signal information is available to any device connected to the serial bus. This information including switch state, block occupancy state, signal state and logic cell state. Switch (turnout) state is called switch messages. Block occupancy state and logic cell state are called sensor messages. The messages carry not only the type, switch or sensor, but the related number or address i.e., switch number or logic cell address.

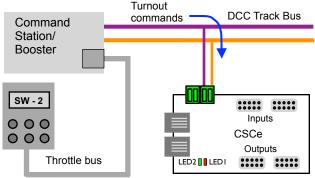

The CSCe logic cells use the information from the serial bus to determine what the signal aspects should be. The result is the CSCe sends signal control messages over the serial bus to the DCC system command station. It converts them to DCC packets which are then put on the track bus. The SHD2s connected to the track bus decode the packets and drive the signal head with the corresponding aspect.

For non-Digitrax systems a DCC gateway feature allows DCC switch command packets to be passed directly to the serial bus. This turns DCC switch command packets into serial bus messages. A special Team Digital signal command station is required in a non-Digitrax system to

convert serial bus messages to DCC packets to control and power the SHD2s.

## **1.1 LED Indicators**

LED 1 flashes indicates Smart programming mode. LED 2 flash indicates accepted program value or a valid received address. LED 3 slow flash indicates heartbeat and fast flash indicates serial bus short.

# 2 Getting Started

You can start using the CSCe without doing any programming. The CSCe comes from the factory programmed to implement a loop with two sidings using Automatic Block Signaling (ABS).

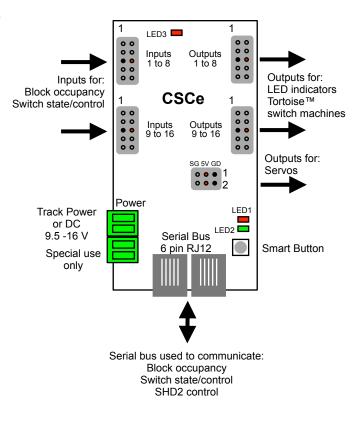

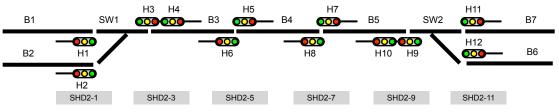

To start using the CSCe to control signals, Signal Head Decoders (SHD2) are required to drive the signal head LEDs. In the diagrams SHD2-x represents a SHD2 driving 2 heads with a related address. The CSCe requires block information from block detectors or occupancy sensors as well as turnout information.

In the diagram a Digitrax system is shown with the basic items needed for operation. Block status information is receive by the CSCe from the BlocD8 via the serial bus. Turnout information is also received by CSCe via the serial bus from the Digitrax system.

If a BlocD8 is not used, then DBD22 block detectors can be used. CSCe input one is assigned to the first block (B1). Connect the DBD22 output used for BI to input one. Connect the other detectors to inputs in sequential order. See the diagram is section 7.1 for wiring information.

A loop like this is probably not what you want to signal. However, we suggest you connect enough items (CSCe, SHD2, signal heads and block detectors) to your system to verify operation before making any changes to the CSCe.

## 2.1 Programming

You will most likely have to program the CSCe to implement the logic you desire. The signal logic information as well as other information is stored in the CSCe using Configuration Variables (CVs). CVs are memory that can be changed by programming.

Programming is done in Operations (Ops) Mode with JMRI DecoderPro via the serial bus. In Ops Mode programming (sometime called On the Main programming) an ops mode address is used to communicate with a particular device. This address (default 10010) is used ONLY for programming and has NOTHING to do with CSCe normal operation.

There are several types of addresses including: DCC Signal decoder addresses as used by the SHD2, turnout addresses, sensor addresses and locomotive decoder addresses. The ops mode programming address is a locomotive type address.

Before actually programming you will need to create a DecoderPro roster entry for a CSCe. Open the 'Service Mode Programmer' then select the Team Digital folder from the list and select CSCe as the decoder type. For the first CSCe go to the 'Roster Entry' tab, enter an ID (e.g. CSCe 10010) and then click on the 'Save to Roster' button. Close this roster entry.

To begin programming open the Operations Mode Programmer and select CSCe 10010, the roster you just saved.

To program additional CSCes it is a good idea to change the ops address. This example shows changing the address to 10020. Disconnect other CSCe from the serial bus. Only connect the CSCe to be programmed.

Go to the Roster menu and select Copy Entry ...., select CSCe 10010 to copy. Enter an id of CSCe 10020.

Open the Operations Mode Programmer and select CSCe 10020, the one you just created.

Go the 'CSCe' tab and enter a 5 digit address in the Ops Mode Address box of 10020. Do not save the roster just yet. Now click 'Write changes on sheet'. The new ops address is written to the CSCes memory.

Then go to the 'Roster Entry' tab, and click the 'Save to Roster' button.

It is important to understand that the CSCe that is having the ops address changed still has an address of 10010. The new address does not take effect until the CSCe power has been cycled. Like wise the roster entries ops address is still 10010 until it has been saved and reopened.

# **3** Operation

## 3.1 Signal Logic

This discussion is basic Automatic Block Signal (ABS) logic. The CSCe uses block addresses, switch (turnout) addresses and DCC signal head addresses (SHD2 addresses) to determine what the signal aspect should be. There are basically three things ahead of the signal head that determine its aspect: block occupancy, next signal state (or signal ahead state) and switch state. The logic and be expressed as a condition(s) with an action - when condition(s) are met then action occurs.

|                                                                                                                                                                                                              | _             | $\rightarrow$ | B1 | B2 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|----|----|

| <b>RED</b> - When the block ahead is occupied then the aspect is red. That is, when B1 is occupied then H1 is red. <i>One condition causes this action</i> .                                                 | -             | H1            | H2 | H3 |

| VELLOW. When the expect is not red and the signal sheed is red then the expect is                                                                                                                            | _             | $\rightarrow$ | B1 | B2 |

| <b>YELLOW</b> - When the aspect is not red and the signal ahead is red then the aspect is yellow. That is, when H1 is not red and H2 is red then H1 is yellow. <i>Two AND conditions cause this action</i> . | -             | H1            | H2 | H3 |

| Note that in this case the block ahead state is not a reliable condition to use. This will be                                                                                                                | _             | $\rightarrow$ | B1 | B2 |

| apparent when a switch is included in the logic.                                                                                                                                                             | -             | H1            | H2 | H3 |

| <b>GREEN</b> - When the aspect is not red and the aspect is not yellow then the aspect is green.                                                                                                             | $\rightarrow$ | B1            | B2 | B3 |

| That is, when H1 is not red and H1 is not yellow then H1 is green. <i>Two AND conditions cause this action</i> .                                                                                             | H1            | H2            | H3 | H4 |

This is a simple way for the CSCe to determine the aspect is green. This will be clearer when programming is discussed.

Some may wish to include flashing yellow as an aspect. The same type of logic is used with an additional logic expression. FLASHING YELLOW - When the aspect is not red and the signal ahead is yellow then the aspect is flashing yellow. That is, when H1 is not red and H2 is yellow then H1 is flashing yellow. Two AND conditions causes this action.

**GREEN** - When H1 is not red and H1 is not yellow and H1 is not flashing yellow then H1 is green. *Three AND conditions* cause this action.

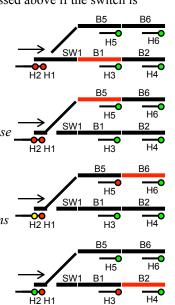

Now lets consider a switch in the logic. A switch directs a train in one of two tracks. If the signal ahead of the switch has two heads, the upper head is for the straight through track and the lower head for the diverging track. Remember the CSCe treats each signal head independently. So the logic for the upper head will be the same as just discussed above if the switch is straight through (closed).

**RED upper** - When the block ahead (straight through) is occupied or the switch ahead is diverging (thrown) then the aspect is red. That is, when B1 is occupied or SW1 is diverging then H1 is red. Two OR conditions cause this action.

When the switch is diverging the upper head is red regardless of B1 or H3.

**YELLOW upper** - When the aspect is not red and the signal ahead is red then the aspect is yellow. That is, when H1 is not red and H3 is red then H1 is yellow. Two AND conditions cause this action.

Note that if B1 had been used as a condition instead of 'H1 is not red', there would be an incorrect aspect.

**GREEN upper** - When the aspect is not red and the aspect is not vellow then the aspect is green. That is, when H1 is not red and H1 is not yellow then H1 is green. Two AND conditions cause this action.

RED lower - When the block ahead (diverging) is occupied or the switch ahead is straight through (closed) then the aspect is red. That is, when B5 is occupied or SW1 is straight then H2 is red. Two OR conditions cause this action.

When the switch is straight the lower head is red regardless of B5 or H5.

YELLOW lower - When the aspect is not red and the signal ahead is red than the aspect is yellow. That is, when H2 is not red and H5 is red then H2 is yellow. Two AND conditions cause this action.

**GREEN** lower - When the aspect is not red and the aspect is not yellow then the aspect is green. That is, when H2 is not red and H2 is not yellow then H2 is green. Two AND conditions cause this action.

Notice that the only time the block and switch states are used is to determine the red aspect. By using the red aspect as a condition for the yellow and green aspects, the logic is simplified.

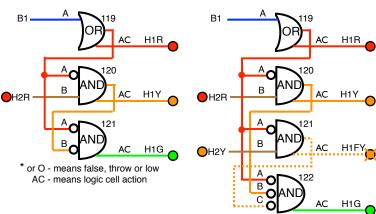

#### 3.2 The Logic Cell

Signal logic requires logic expressions in order for the signals to work correctly. The CSCe logic cells implement those logical expressions. Each logic cell contains three conditions: A, B and C. Each condition can contain information about a block, switch or signal state. Logical operators OR and AND are used to connect the logic conditions together. So, for example, if condition A OR condition B is true,

| Logic Combination | B Logic | C Logic |

|-------------------|---------|---------|

| A OR B OR C       | OR      | OR      |

| (A OR B) AND C    | OR      | AND     |

| (AAND B) OR C     | AND     | OR      |

| A AND B AND C     | AND     | AND     |

then perform an action. If a switch is thrown OR the block is occupied then the signal head aspect is red. Conditions B and C can be combined with condition A in AND and OR logic combinations by using the logic selection in conditions B and C. When the logic combination is satisfied, the logic cell is true and its action is performed.

The CSCe has 66 logic cells and each cell has an address. The logic cell addresses are sequential starting at 101 (factory setting) for logic cell one (1). A logic condition includes an address, type and state. The types are: sensor (for a block), sensor (for a logic cell), switch request, switch feedback or DCC signal. Different types can have the same address. However, since blocks and logic cells use sensor type addresses, be sure there are no duplicate sensor addresses.

When a logic cell action is performed a message is send on the serial bus. SHD2s are controlled by DCC Signal messages. Messages on the serial bus are available to all CSCes connected to the bus. Whenever a logic cell changes state a sensor type message indicating its state is available to all logic cells. Optionally it can be sent on the serial bus.

Shown below are three logic cells from a DecoderPro roster entry used in programming the CSCe. The entry shows the logic for H1 used for the example in the first part of the Signal Logic discussion. Each logic cell controls a signal head aspect. If a condition has an address of zero (0) and an operator of OR it will be ignored by the logic cell. An address of zero (0) and an operator of AND will give an unexpected result. An action is not performed if its address is zero (0).

| Logic Cell 19 119 Logic cell 19 - when B1 is occupied then H1 is red                  |                                  |

|---------------------------------------------------------------------------------------|----------------------------------|

| Condition A Address 1 Type DCC Signal 🗌 Sensor 🛟 State False (Throw or Low) 🛟         | Action when logic cell goes True |

| B Logic OR 🗧 B1 address                                                               | DCC Signal 🗹                     |

| Condition B Address 0 Type DCC Signal 🗌 Switch Request 🗘 State False (Throw or Low) 🗘 | Address 1                        |

| C Logic OR 🗘 H1 addres                                                                | S Aspect 0-Red                   |

| Condition C Address 0 Type DCC Signal 🗌 Switch Request 🛟 State False (Throw or Low) 🛟 |                                  |

| Logic Cell 20 120 Logic cell 20 - when H1 is not red and H2 is red then H1 is yellow  | N                                |

| Condition A Address 119 🚤 Type DCC Signal 🗌 Sensor 🛟 State False (Throw or Low) 🛟     | Action when logic cell goes True |

| B Logic AND Cogic cell 19 address                                                     | DCC Signal 🗹                     |

| Condition B Address 2 🚤 Type DCC Signal 🗹 Aspect 0-Red 🛟                              | Address 1                        |

| C Logic OR 🛟 H2 address                                                               | Aspect 1-Yellow                  |

| Condition C Address 0 Type DCC Signal 🗌 Switch Request 💠 State False (Throw or Low) 🛟 |                                  |

| Logic Cell 21 121 Logic cell 21 - when H1 is not red and H1 is not yellow then H1     | s green                          |

| Condition A Address 119 Type DCC Signal 📃 Sensor 🗘 State False (Throw or Low) 🛟       | Action when logic cell goes True |

| B Logic AND                                                                           | DCC Signal 🗹                     |

| Condition B Address 120 Type DCC Signal Sensor State False (Throw or Low)             | Address 1                        |

| C Logic OR 🗧 Logic cell 20 address                                                    | Aspect 2-Green                   |

| Condition C Address 0 Type DCC Signal C Switch Request State False (Throw or Low) 🗘   |                                  |

DecoderPro address fields can have different colors: white to indicate a confirmed CSCe value, yellow to indicate a nonconfirmed CSCe value and orange to indicate a changed value. Red is used to indicate some type of an error like not successfully programmed. Logic symbols can be used to show logic expressions. Here is a couple of diagrams showing the logic for H1. The diagram with four logic cells includes flashing yellow.

CSCe logic cell evaluation occurs in a sequence of lower to higher numbered cells. For example the action of logic cell 119 (H1R) occurs before the action of logic cell 120 (H1Y). It is import to understand this when doing sequential logic. This is independent of how logic cells are connected to each other.

#### 3.4 Logic Cell Base Address

The logic cell state base address is located in the CSCe tab. Whenever a logic cell changes state a message is sent indicating its state. The address of this message is determined by the base address. The address of logic cell 1 is the base address. The address of logic cell 2 is the base address plus 2 etc.

The default base address is 101. It does not typically need to be changed. If you change this address any logic cells programming using Conditions with logic cell addresses will also have to be changed.

#### 3.5 CSCe Configuration

Configuration is located in the CSCe tab.

**Ops Mode:** Allows Operations mode (On the Main) programming. Default: enabled

**Ops Mode Address:** Operations mode (On the Main) programming address. This address is used ONLY for programming and has NOTHING to do with normal operation. This allows programming the CSCe just like you would a loco in ops mode. This is a loco address and therefore must be unique among locomotive addresses. Default: address 10010

**Logic cell state messages:** Enables the logic cell output state messages to be put on the serial bus. May be useful in analyzing logic cell operation. Default: disabled

**DCC gateway:** Allows DCC switch command packets to be put on the serial bus. Any device connected to the bus will have access to these DCC commands.

**Note:** If there are more than one CSCe or other gateway capable devices, only one should have the gateway enabled. In a Digitrax system **DO NOT** connect the CSCe to the throttle LocoNet if the gateway is enabled. This could cause an endless sending of switch commands from the track to LocoNet and back to the track. Default: disabled

| Configuration                                                                 |

|-------------------------------------------------------------------------------|

| Ops Mode Yes 🛟                                                                |

| Ops Mode Address 10010                                                        |

| This is the same as a Loco address                                            |

| Logic Cell State Msg No 🛟<br>Send output state on serial bus                  |

| DCC gateway 🛛 No 🛟                                                            |

| Pass DCC switch commands on to serial bus                                     |

| Interrogate inputs No 🛟<br>Send input state at Digitrax interrogation request |

| Common Cathode LEDs No 🛟                                                      |

| Use common cathode LEDs on all outputs                                        |

----- Logic Cell Addresses ----

Logic Cell State Base Address 101

**Interrogate inputs:** Input state messages are put on the serial bus when a Digitrax interrogation command is received. Default: disabled

**Common cathode LEDs:** Allows common cathode connection of LEDs to the outputs. Default: disabled

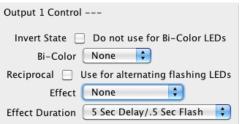

#### 3.6 Output Control

Output Control determines how the output will respond when it is turned on. Logic cells 1 to 16 each have a physical output 1 to 16 respectively. When a logic cell is true the output is "turned on" or grounded. When the logic cell is false the output is "turned off" or at 5 volts. Typically an output would be used to drive a LED to indicated block (occupancy) or switch (turnout) position. Also it could be used to drive a Tortoise<sup>™</sup> switch machine.

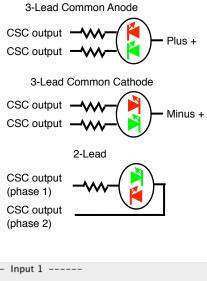

**Invert State:** The normal state for the outputs is to drive common anode LEDs. Use Invert State if you want to use a common cathode connected LED. If you want to change all the outputs set Common cathode in Configuration.

**Bi-color:** LEDs with two leads require two outputs as shown in figure 11. Set one of the output control CVs to phase 1 and the other to phase 2. This gives the CSCe the ability to display three colors.

**Effect:** has three selections. Delay causes the output to delay turn on once the logic cell is true. This can be used to delay the grade crossing gate lowering from the time the flashers start. Flash causes the output to flash whenever the logic cell is true. Dynamic flash works only with logic condition C. If the logic cell is true due to either logic condition A or B the output will be on. If logic condition C becomes true then the output will flash.

**Reciprocal:** is used only with the flash effect to cause two outputs to flash alternately. Both outputs have to be selected to flash with the same duration. One of the outputs is selected for reciprocal. This can be used for grade crossing flashers.

**Effect Duration:** works only when one of the effects is selected. It determines the flash rate and delay time.

#### 3.7 Input Control

The input control determines what action an input will have. Typically an input would be connected to a block (occupancy) detector or a switch (turnout) position indicator. A push button or toggle switch could also be connected to cause some action to occur. There are 16 physical inputs.

Address: A number to uniquely define the item connected to the input. For example, each block must have a number.

**Toggle:** Only available when the type message is switch request. Typically used when a push button is connected to control a turnout.

**Type:** The type of message an input will send on the serial bus when a transition occurs. Select sensor to send a message with the block address and occupied status. Select switch feedback to send a message with the switch address and state. Select switch request to send a message to control a turnout with switch address and state.

**Invert:** This inverts the state of the input that the input message contains. Use this when a block detector is connected to a input. For example, when a DBD22 in connected to a CSCe input, the input will go low when the block is occupied. The message should indicate a HI for block occupied not LOW.

**Transition:** In order for an input to cause an action a transition must be selected. The input is normally at 5 volts. An input transition occurs when the voltage on an input goes from high to low (falling edge) or from low to high (rising edge). For example, if a compatible occupancy (block) detector is connected to an input and the block becomes occupied, the input is grounded. This causes a high to low transition. When the block becomes unoccupied this causes a low to high transition.

**Delay:** This delay determines how long the CSCe waits to show an input low to high transition from when it actual occurs. A delay is typically used when a block detector is connected to a input to increase the time from when the block actually becomes unoccupied to when the CSCe reports it is unoccupied. Value x 256 ms = approx. delay. Default is 0.

#### Bi-Color LEDs

| Input        | 1        |        |   |        |   |

|--------------|----------|--------|---|--------|---|

| Address 1    | 11       | Toggle |   |        |   |

| Туре         | 1 Sensor |        | + | Invert | ☑ |

| Transition 1 | +        |        |   |        |   |

| Delay 1      | 0        |        |   |        |   |

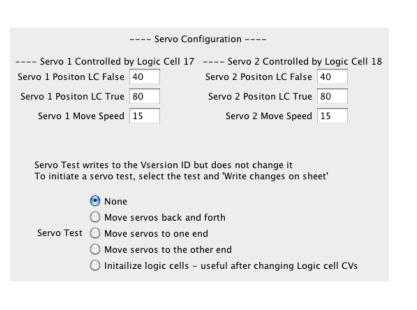

#### 3.8 Servo Configuration

Servo configuration is located in the Servos tab. There are two servo outputs each controlled by a logic cell. Logic cells 17 and 18 each control a servo.

**Servo Position LC False:** The position the servo moves to when the logic cell is false. Values can be 1 to 127.

**Servo Position LC True:** The position the servo moves to when the logic cell is true. Values can be 1 to 127.

**Servo Move Speed:** The speed in which the servo moves. Values can be 1 to 127.

**Servo Test:** This allows the servos to be positioned without a logic cell change.

#### 3.9 Logic Cell Delay

| Logic Cell Delay is located in the Logic Cell 57-64 Delay tab. This delay determines how |

|------------------------------------------------------------------------------------------|

| long the CSCe waits to show a logic cell state change from when it actual occurs.        |

| Value x 256 ms = approx. delay. Default is 0.                                            |

----- Logic Cell 57 -----LC Delay 57 0

An application of this is used in the grade crossing Setup to delay the lowering of the gates from the time the lights start to flash.

# 4 Setup

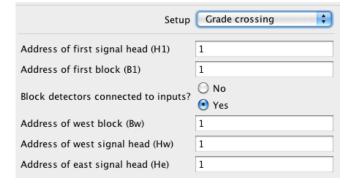

Setup selection is located in the DecoderPro Setup tab. The CSCe has several built-in signal arrangements called Setups that can be implemented without any custom programming.

These can be considered as examples to help learn about the CSCe because in most cases none of the setups will be what you are looking for. However, you can start with a setup that has some of the features you want and then experiment. To experiment, read the CVs into JMRI and modify the logic.

After a setup is chosen, determine if the CSCe inputs will be used and how LEDs are connected to the outputs. Inputs are available for block detectors and push buttons. Outputs are available for block occupancy and turnout state LED indication. Typically blocks are assigned with block 1 stating at input/output 1. Turnouts are assigned with turnout 1 stating at input/output 9. See section 6.4 for the relationship between the connector, the connector pin number, and the output number.

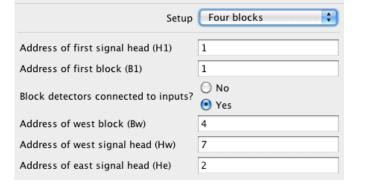

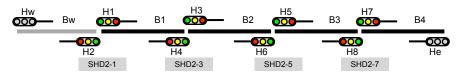

#### 4.1 Setup 1 - Four blocks

This setup implements four blocks of bi-directional travel with eight signal heads using ABS logic. The diagram below shows the block arrangement and how the signal heads and blocks are assigned. Multiple CSCes can easily work together by setting the correct block and head addresses. Head addresses are the signal head addresses of the SHD2s. SHD2-1 drives heads H1 and H2. SHD2-3 drives heads H3 and H4 ... etc. All addresses are sequentially assigned starting with the address you enter. There are 4 blocks.

Address of first signal head (H1): This is the address of the first SHD2 (SHD2-1).

Address of first block (B1): This is the address of the first block.

**Block detectors connected to inputs?:** Will DBD22 block detectors be connected to the CSCe inputs. If yes, then input one is assigned to the first block (B1). Connect the DBD22 output used for BI to input one. Connect the other detectors to inputs in sequential order. If no, then the CSCe will expect to receive block status over the serial bus.

Address of west block (Bw): This is the address of the block just west of B1.

Address of west signal head (Hw): This is the address of the head just east of H8.

Address of east signal head (He): This is the address of the head just west of H1.

LEDs can be connected to Outputs 1 to 4 to indicated block status.

A loop can be implemented by setting the address of west block (Bw) to the same as B4, the address of west head (Hw) to the same as H7 and the address of east head (He) to the same as H2 (H2 is the address of H1 plus 1). Using the diagram below with four blocks in a circle would mean Bw is B4, Hw is H7 and He is H2.

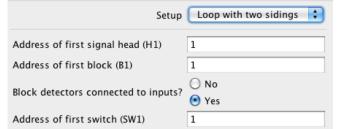

#### 4.2 Setup 2 - Loop with two sidings

This setup implements a loop with two sidings using Automatic Block Signaling (ABS). The diagram below shows the block arrangement and how the signal heads and blocks are assigned. Head addresses are the signal head addresses of the SHD2s. All addresses are sequentially assigned starting with the address you enter. There are 6 blocks.

Address of first signal head (H1): This is the address of the first SHD2 (SHD2-1).

Address of first block (B1): This is the address of the first block.

#### **Block detectors connected to**

N9 H10 inputs: Will DBD22 block SW1 000 B3 SW2 00000 detectors be connected to the 000 CSCe inputs. If yes, then input 00000 H6 000 B2 H7 H4 H3 one is assigned to the first block (B1). Connect the 000 DBD22 output used for B1 to H8 SHD2-3 SHD2-5 SHD2-7 SHD2-9 input one. Connect the other B1 Β4 H16 detectors to inputs in sequential 000 B6 order. If no, then the CSCe will expect to receive block status 000 H15 N11 H12 over the serial bus. B5 H14 00000 000 SW4 000 SW3 **00000 Address of first switch** H2 H1 H13 (SW1): This is the address of SHD2-15 SHD2-11 SHD2-1 SHD2-13 the first switch.

LEDs can be connected to Outputs 1 to 6 to indicated block status. LEDs can be connected to Outputs 9 to 16 to indicated switch status.

#### 4.3 Setup 3 - APB signals

This setup implements a section track using Absolute Permissive Block (APB) signaling. The diagram below shows the block arrangement and how the signal heads and blocks are assigned. Head addresses are the signal head addresses of the SHD2s. All addresses are sequentially assigned starting with the address you enter. There are 7 blocks.

Address of first signal head (H1): This is the address of the first SHD2 (SHD2-1).

Address of first block (B1): This is the address of the first block.

| Setup                                | APB signals   |

|--------------------------------------|---------------|

| Address of first signal head (H1)    | 1             |

| Address of first block (B1)          | 1             |

| Block detectors connected to inputs? | ○ No<br>● Yes |

| Address of first switch (SW1)        | 1             |

**Block detectors connected to inputs?:** Will DBD22 block detectors be connected to the CSCe inputs. If yes, then input one is assigned to the first block (B1). Connect the DBD22 output used for BI to input one. Connect the other detectors to inputs in sequential order. If no, then the CSCe will expect to receive block status over the serial bus.

Address of first switch (SW1): This is the address of the first switch.

LEDs can be connected to Outputs 1 to 7 to indicated block status. LEDs can be connected to Outputs 9 to 12 to indicated switch status.

#### 4.4 Setup 4 - Grade crossing

This setup implements four blocks of bi-directional travel with eight signal heads using ABS logic. The diagram below shows the block arrangement and how the signal heads and blocks are assigned. Multiple CSCes can easily work together by setting the correct block and head addresses. Head addresses are the signal head addresses of the SHD2s. SHD2-1 drives heads H1 and H2. SHD2-3 drives heads H3 and H4 ... etc. All addresses are sequentially assigned starting with the address you enter. There are 4 blocks.

Address of first signal head (H1): This is the address of the first SHD2 (SHD2-1).

Address of first block (B1): This is the address of the first block.

**Block detectors connected to inputs?:** Will DBD22 block detectors be connected to the CSCe inputs. If yes, then input one is assigned to the first block (B1). Connect the DBD22 output used for BI to input one. Connect the other detectors to inputs in sequential order. If no, then the CSCe will expect to receive block status over the serial bus.

Address of west block (Bw): This is the address of the block just west of B1.

Address of west signal head (Hw): This is the address of the head just east of H8.

Address of east signal head (He): This is the address of the head just west of H1.

LEDs can be connected to Outputs 1 to 6 to indicated block status.

EB Approach Island WB Approach Typical operation: Upon entering an Hw H1 H3 H5 H7 Bw B1 000 B2 B3 B4 B5 B6 000 000 000 000 approach the bell and 000 000 000 flashing cross buck with 000 H2 H4 H6 H8 He the gate lowered a little SHD2-3 SHD2-1 SHD2-5 SHD2-7 later. When the island is

cleared the bell and flashing stop and the gate is raised.

The CSCe provides outputs to enable a bell sound and alternately flash the cross buck LEDs. Also there are two outputs to drive a Tortoise<sup>TM</sup> and two to drive servos which can be used to move the crossing gate. Logic Cell 64 delay is used for the crossing gate delay. This delay can be changed. See section 3.9.

#### Requirements for proper operation:

The approach block must show occupied as long as the train is in it or the signal flashing will not work correctly. This can be achieved if each train is not longer than the approach block or the train has enough resistive wheels. The approach block must be occupied when the island block becomes occupied.

# **5** Special Features

#### 5.1 Reset the CSCe to factory defaults

To "reset" the CSC to factory defaults, turn power on and wait until LED 1 turns off. Then press the "Smart" button and continue to hold the button down (at least 16 seconds) until both LED 1 & 2 are alternately flashing. Or, programming CV7 with 170 will "reset" all CV's to the factory default value.

#### 5.2 Temporary Ops Mode

If ops mode is not enabled in the CSC configuration, it can be put into that mode temporarily at power on. Hold down the Smart button just before power is turned on. When the green LED turns on release the button then wait until the red LED turns off. The CSC is now in ops mode until power is turned off. This is useful if you do not want to have ops mode enabled all the time.

#### 5.3 Set Ops Mode Address

The ops mode address can be set to the default address of 10010 or to a higher address number. This may be useful if, for some reason, you do not know the ops address of the CSCe and do not want a complete reset.

Connect the CSCe to track power. Turn power on and wait until LED 1 turns off. Then press the "Smart" button and hold the button down (about 1 second) until LED 1 is flashing.

To "reset" the CSCe ops mode address to the default address of 10010, use the throttle and select turnout (switch) address 1 and issue a "t" command.

To set the CSCe ops mode address to a higher number, use the throttle and select a turnout (switch) address that is the amount greater than 10010 you want and issue a "c" command. For example, to set the ops address to 10020, select a turnout address of 10 and issue a "c"ccommand. Turnout

After the command has been issued the CSCe will restart with the new ops mode address.

Note: "throttle" refers to any device that can issue or send switch commands. "c" refers to Close or Normal switch position. "t" refers to Throw or Reverse switch position.

# **6** Connections

#### 6.1 Power

The CSCe is powered by using the two terminal connector labeled Power. See diagram section 6.4. Power can be from the track (14 V max) or a DC power supply (9.5 to 14 V). For a DC supply do not use old analog 'Power Packs'. The CSCe power connector is non polarized and either terminal can be connected to plus or minus of the DC power supply. The power supply should be isolated from the system ground. That is, not connected to ground (booster ground, house wiring ground, etc). When multiple CSCes are used they can be all connected to one power supply. The plus and minus of the power supply must be connected to the same power input terminal on each CSCe.

Power supply current requirements: 9.5 to 14 V, 300mA minimum.

#### 6.2 Input Interface

Each input has a 4.7K 'pullup' resistor connected to 5 volts, so the input is normally at 5 volts with respect to pin 5 (minus) when no device is connected. This is a high or true state. When the input is connected to pin 5 (minus) by a push button switch or block sensor, the input is "grounded" and the state is low or false.

### 6.3 Output Drive

The output supplies about 5 volts to drive LEDs and Tortoise<sup>TM</sup> switch machines. If LEDs are used current limiting resistors are required and should not be less the 470 ohms. This is a general guide line for a typical LED. The current limit for any single output is 20 mA and the total of any connector group of eight outputs is 50 mA. Typically all output are not on at one time.

#### 6.4 Input and Output Pins

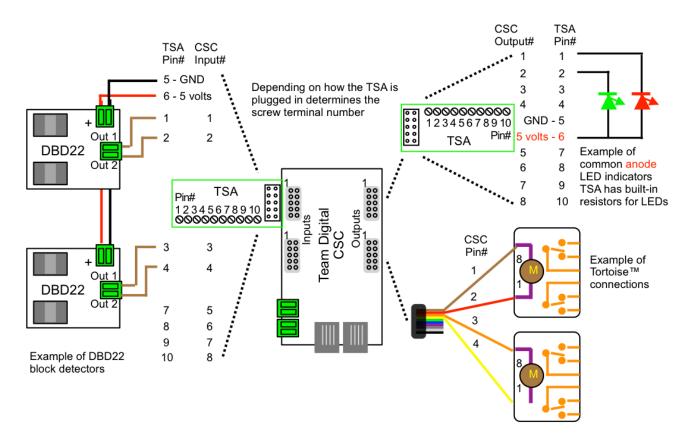

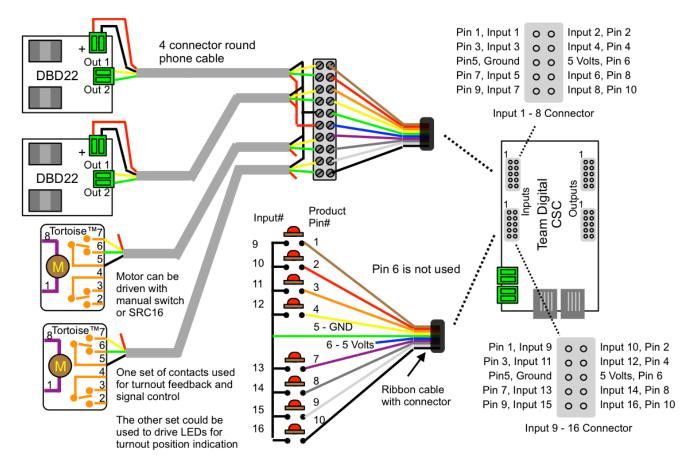

Input and output connectors have the same pin definitions. Connections can be made using our terminal strip adapter (TSA) or our Connector Cable Kit. You can build your own by using flat ribbon cable Insulation Displacement (IDC) and connectors from Jameco. The mating connector is #138376. 10 ft of multicolor flat ribbon cable is #639672. See the diagram on the front page for connector location.

Warning: Do not connect the power supply ground (minus) to the ground (minus) pin 5 of the 10 pin IDC connector. Do not connect any outputs together or to other CSCe outputs. Do not (plus) pin 6 to other CSCes.

| Input 1 - pin 1  | 00  | Input 2 - pin 2   | Output 1 - pin 1  | 00   | Output 2 - pin 2  |

|------------------|-----|-------------------|-------------------|------|-------------------|

| Input 3 - pin 3  | 00  | Input 4 - pin 4   | Output 3 - pin 3  | 00   | Output 4 - pin 4  |

| Minus - pin 5    | • • | 5 Volts - pin 6   | Minus - pin 5     | • •  | 5 Volts - pin 6   |

| Input 5 - pin 7  | 00  | Input 6 - pin 8   | Output 5 - pin 7  | 00   | Output 6 - pin 8  |

| Input 7 - pin 9  | 00  | Input 8 - pin 10  | Output 7 - pin 9  | 00   | Output 8 - pin 10 |

|                  |     |                   |                   |      |                   |

|                  |     |                   |                   |      |                   |

| Input 9 - pin 1  | 00  | Input 10 - pin 2  | Output 9 - pin 1  | 00   | Output 10 - pin 2 |

| Input 11 - pin 3 | 00  | Input 12 - pin 4  | Output 11 - pin 3 | 00   | Output 12 - pin 4 |

| Minus - pin 5    | • • | 5 Volts - pin 6   | Minus - pin 5     | • •  | 5 Volts - pin 6   |

| Input 13 - pin 7 | 00  | Input 14 - pin 8  | Output 13 - pin 7 | 00   | Output 14 - pin 8 |

| Input 15 - pin 9 | 00  | Input 16 - pin 10 | Output 15 - pin 9 | 00   | Output 16 - pin   |

|                  |     |                   |                   |      |                   |

|                  |     |                   |                   |      |                   |

|                  |     |                   |                   |      |                   |

| Track Power      |     | 1                 | Servo 1 - S       | 5V G |                   |

| or 9.5 -14 VDC   |     |                   |                   | •    | S - Signal        |

|                  |     | <u>,</u>          |                   |      | 5V - 5            |

| Special use      |     | 1                 | 0                 | • •  | volts             |

The servo connector has the standard 3 pins per servo.

0

only

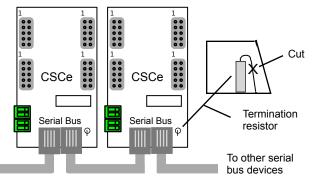

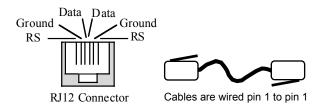

## 6.5 Serial Bus

The CSCe has two RJ12 connectors for ease in making connections as shown below. In a Digitrax system the data pins are LocoNet and the RS pins are Rail Sync. In a Digitrax system Rail Sync is a replica of the track power signal but has limited power. One of its uses is to provide power to throttles connected to LocoNet. In the CSCe the RS is only connected to the two terminal Special use connector.

In some cases the RS may be used to pass power from one CSCe to another. Do NOT use the rail sync terminals if any CSCe is driving servos or in a standard Digitrax system if the CSCes are connected to the main LocoNet bus.

In a systems when more than 10 Team Digital products are connected to the serial bus, the bus terminating resistor should be cut on any additional devices.

# 7 Wiring Diagram

### 7.1 Wiring Examples

These diagrams show examples of wiring for a number of devices that can be used with the CSCe. The TSA is a terminal strip adaptor that plugs into the CSCe 10 pin connector to provide screw terminals. They also have built-in resistors so LEDs can be easily connected to the CSCe outputs. DBD22s can also be wired via TSAs or via a ribbon as shown below.

Additional example of input wiring. Inputs can be used for DBD22s, turnout feedback from switch machines and push button control of turnouts as shown or for connection to turnout contacts for turnout feedback.

# 8 Reference

## 8.1 Selected CVs

This chart shows some CV numbers and their default values.

| CV# | Function/Default Value         |     |  |  |  |

|-----|--------------------------------|-----|--|--|--|

| 1   | Ops Mode Loco Address          | 26  |  |  |  |

| 2   | Ops Mode Loco Address Adder    | 39  |  |  |  |

| 3   | Base Address                   | 101 |  |  |  |

| 4   | Base Address Adder             | 0   |  |  |  |

| 5   | Base Signal Head Address       | 1   |  |  |  |

| 6   | Base Signal Head Address Adder | 0   |  |  |  |

| 7   | Manufacturer Version No.       | -   |  |  |  |

| 8   | Manufacturer ID                | 25  |  |  |  |

| 9   | Configuration                  | 1   |  |  |  |

|     |                                |     |  |  |  |

|     |                                |     |  |  |  |